��(d��ng)ǰλ�ã����(y��) > �W(xu��)��(x��)�YԴ > �v������ > ����Arm Cortex-M55��������AIָ��U(ku��)չ�c�����{(di��o)��(y��u)��(sh��)�`

����Arm Cortex-M55��������AIָ��U(ku��)չ�c�����{(di��o)��(y��u)��(sh��)�`

�r(sh��)�g��2025-04-23 ��(l��i)Դ���A���h(yu��n)Ҋ(ji��n)

����Arm Cortex-M55��������AIָ��U(ku��)չ�c�����{(di��o)��(y��u)��(sh��)�`

�r(sh��)�g��2025-04-23 ��(l��i)Դ���A���h(yu��n)Ҋ(ji��n)

����

�S��߅��Ӌ(j��)�����(li��n)�W(w��ng)��IoT���Ŀ��ٰl(f��)չ��Ƕ��ʽ�O(sh��)�䌦(du��)�˹����ܣ�AI���͙C(j��)���W(xu��)��(x��)��ML����֧�������������L(zh��ng)��Arm Cortex-M55 �������{��������ܡ����ĺ͌�(zhu��n)��AI�����������ɞ�߅��AI��(y��ng)�õ����xƽ�_(t��i)�����Č��������Cortex-M55��AIָ��U(ku��)չ�������� Helium �� AI-NPU�������Y(ji��)�ό�(sh��)�H����̽ӑ�������{(di��o)��(y��u)�����������_(k��i)�l(f��)�߸�Ч�����@һ�ܘ�(g��u)��(sh��)�F(xi��n)߅��AI��(y��ng)�á�

һ��Cortex-M55��AIָ��U(ku��)չ��Helium�cAI-NPU

1.1 Helium������Mϵ�е������U(ku��)չ

Helium��MVE��Matrix Vector Extension�� ��Arm��Cortex-Mϵ���O(sh��)Ӌ(j��)��ȫ��SIMD����ָ�����(sh��)��(j��)��ָ��U(ku��)չ��ּ�ڞ�Ƕ��ʽ�O(sh��)���ṩ��Ч��AI����̖(h��o)̎���������������������

· 150+��ָ�����130+ʸ��ָ�֧������(sh��)���c(di��n)�\(y��n)�㡣

· 128λ�����Ĵ�����8��(g��)�����Ĵ�����V0-V7����ÿ��(g��)�Ĵ�����ӳ�䵽4��(g��)FPU�Ĵ�������������c��e��(y��u)����

· ��(sh��)��(j��)�(l��i)��֧�֣�

o ����(sh��)��8�16�32�

o ���c(di��n)���뾫�ȣ�FP16�����ξ��ȣ�FP32�����p���ȣ�FP64����

· �pģʽ�U(ku��)չ��

o MVE-I���H֧������(sh��)�\(y��n)�㡣

o MVE-F��֧������(sh��)���c(di��n)�\(y��n)�㡣

��(du��)��Neon��

Helium���Neon���p������ᘌ�(du��)���Ĉ�(ch��ng)����(y��u)������֧��8λ����(sh��)�Ͱ뾫�ȸ��c(di��n)�\(y��n)�㣬���m��AIģ���еľ��e������\(y��n)��Ȳ�����

1.2 AI-NPU����(zhu��n)����(j��ng)�W(w��ng)�j(lu��)������

Cortex-M55�ɼ��� AI-NPU����(j��ng)�W(w��ng)�j(lu��)̎��������ͨ�^(gu��)Ӳ�������M(j��n)һ������AI�������ܡ��䃞(y��u)��(sh��)������

· ����Ч�ȣ���ȼ�CPUӋ(j��)�㣬NPU�Ɍ�AI�����ٶ�������(sh��)����ͬ�r(sh��)�����ġ�

· ֧������ģ�ͣ�����TensorFlow Lite Micro��Arm Ethos-U NPU�ȿ�ܣ���(ji��n)��ģ�Ͳ���

· �`�����ã�������MAC��Ԫ��(sh��)������(n��i)�控���ȅ���(sh��)���m�䲻ͬ��������

����Cortex-M55�ļܘ�(g��u)���c(di��n)�c���܃�(y��u)��(sh��)

2.1 ���ļܘ�(g��u)

Cortex-M55���� ARMv8.1-M�ܘ�(g��u)������ 4��(j��)�����(bi��o)����ˮ����֧�������P(gu��n)�I���ԣ�

· �pָ���a����ͬ�r(sh��)��a�ɂ�(g��)������16λT16ָ�������������

· �f(xi��)̎�����ӿڣ�֧���Զ��xָ��U(ku��)չ����AI-NPU��������(qi��ng)�`���ԡ�

· ���܌�(du��)�ȣ�

o CoreMark/MHz��4.2����Cortex-M4��25%��������Cortex-M7�s20%��

o �l�ʣ���M4��15%����������ˮ���L(zh��ng)�ȣ��o(w��)���cM7�ij���(bi��o)���O(sh��)Ӌ(j��)ƥ������

2.2 �����x�(xi��ng)

Cortex-M55�ṩ��N���ã��_(k��i)�l(f��)�߿ɸ���(j��)�����x��

· ���A(ch��)���ã��H����(sh��)��ˮ����

· FPU֧�֣����Ӹ��c(di��n)�\(y��n)��������

· Helium�U(ku��)չ������(sh��)������MVE-I�������c(di��n)������MVE-F������߽Y(ji��)�ϡ�

���������{(di��o)��(y��u)��(sh��)�`

3.1 ��������(y��u)����Helium��

3.1.1 ����ָ���ʹ��

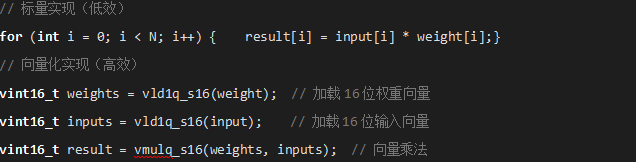

ͨ�^(gu��)Helium��MVEָ��Ɍ���(bi��o)���\(y��n)���D(zhu��n)�Q�������\(y��n)�㣬�@���������������磬��(du��)�D��(sh��)��(j��)�ľ��e������

3.1.2 ��(n��i)�挦(du��)�R�c�A(y��)ȡ��(y��u)��

· ��(sh��)��(j��)��(du��)�R���_�����������Ĕ�(sh��)��(j��)�ڃ�(n��i)���Ќ�(du��)�R��16�ֹ�(ji��)߅�磬�������ܓpʧ��

· �A(y��)ȡָ�ʹ��PLD���A(y��)ȡ��(sh��)��(j��)��ָ����ǰ���d���m(x��)��(sh��)��(j��)���p�پ������t��

3.2 AI-NPU�������c�{(di��o)��(y��u)

3.2.1 ģ�������c���s

· ��������FP32ģ���D(zhu��n)�Q��INT8��FP16��ʽ�����̓�(n��i)��ռ�ú�Ӌ(j��)���(f��)�s�ȡ�

· ��֦�c���s��ͨ�^(gu��)ģ�͉��s���g(sh��)�p�م���(sh��)�����m��߅���O(sh��)����YԴ���ơ�

3.2.2 NPU�cCPU�f(xi��)ͬӋ(j��)��

· �΄�(w��)���䣺����(f��)�sӋ(j��)�㣨����e�����oNPU����(ji��n)��߉������CPU̎����

· ��(n��i)���������������N(xi��o)PU��(zhu��n)�Ã�(n��i)�棬���┵(sh��)��(j��)��CPU��NPU�g���l����ؐ��

3.3 �ܺă�(y��u)��

· ��(d��ng)�B(t��i)늉��c�l���{(di��o)��(ji��)��DVFS��������(j��)ؓ(f��)�d��(d��ng)�B(t��i)�{(di��o)��CPU�l�ʺ�늉���ƽ�������c���ġ�

· ˯��ģʽ���ڷ�Ӌ(j��)���A���M(j��n)�����ģʽ����Sleep-on-Exit����

�ġ���(sh��)�H����������Cortex-M55���Z(y��)���R(sh��)�e����

4.1 ��(ch��ng)������

����һ��(g��)���� TensorFlow Lite Micro ���P(gu��n)�I�~�z�y(c��)ģ�ͣ���“�����~�R(sh��)�e”����Ҫ��

· ���ģ�����100mW��

· ���t��푑�(y��ng)�r(sh��)�g<50ms��

4.2 ��(y��u)�����E

1. ģ��������

o ��FP32ģ���D(zhu��n)�Q��INT8��ʽ���p�ك�(n��i)��ռ�á�

2. ���������٣�

o ʹ��Helium��MVE-Fָ�(y��u)����̖(h��o)�A(y��)̎������FFT����

3. NPU���٣�

o �����e�ӽ���NPU̎����CPUؓ(f��)؟(z��)��(sh��)��(j��)�A(y��)̎���ͺ�̎����

4. ��(n��i)�惞(y��u)����

o ʹ��SRAM�������g�Y(ji��)���������l���L��(w��n)Flash��

4.3 �Y(ji��)��

· ���������������ٶ�����3�������Ľ���40%��

· 푑�(y��ng)�r(sh��)�g����(w��n)����30ms��?x��n)?n��i)���M�㌍(sh��)�r(sh��)��Ҫ��

�塢���Y(ji��)�cչ��

Cortex-M55ͨ�^(gu��) Helium�����U(ku��)չ �� AI-NPU����Ƕ��ʽAI�ṩ�ˏ�(qi��ng)��������c��Ч�ȡ��_(k��i)�l(f��)����Y(ji��)�����²��Ԍ�(sh��)�F(xi��n)�������

1. �������������ָ��p�٘�(bi��o)���\(y��n)�㡣

2. ��������NPU�cCPU���΄�(w��)�ֹ���ƽ���YԴ���á�

3. ��ȃ�(y��u)����(n��i)���c���Ĺ������_�������t�c���ġ�

δ��(l��i)���S�� Arm Ethos-U NPU ���M(j��n)һ�����ɺ���朵����ƣ�Cortex-M55����߅��AI�I(l��ng)��l(f��)�]���������Ƅ�(d��ng)����(f��)�sģ�ͣ����p����(j��)CNN��Transformer�������

�n�̷������A���h(yu��n)Ҋ(ji��n)(li��n)��NXP�Ƴ�i.MX8M Plus�_(k��i)�l(f��)�c��(sh��)�`

�n�̷������A���h(yu��n)Ҋ(ji��n)(li��n)��NXP�Ƴ�i.MX8M Plus�_(k��i)�l(f��)�c��(sh��)�` �n�̷���������HarmonyOSϵ�y(t��ng)����(li��n)�W(w��ng)�_(k��i)�l(f��)��(sh��)��(zh��n)�n�̣�

�n�̷���������HarmonyOSϵ�y(t��ng)����(li��n)�W(w��ng)�_(k��i)�l(f��)��(sh��)��(zh��n)�n�̣� �n�̷�����HaaS EDU K1�_(k��i)�l(f��)�̳̣����n��ҕ�l��Դ�a��

�n�̷�����HaaS EDU K1�_(k��i)�l(f��)�̳̣����n��ҕ�l��Դ�a�� �°�C�Z(y��)�Ծ���֮�����Z(y��)��ҕ�l�̳��ذ�ٛ(z��ng)�ͣ�Ƕ��ʽ��

�°�C�Z(y��)�Ծ���֮�����Z(y��)��ҕ�l�̳��ذ�ٛ(z��ng)�ͣ�Ƕ��ʽ�� �r(ji��)ֵ2000Ԫ��Ƕ��ʽ���b�̴̳�Y�����M(f��i)�ͣ����㶮Ƕ��

�r(ji��)ֵ2000Ԫ��Ƕ��ʽ���b�̴̳�Y�����M(f��i)�ͣ����㶮Ƕ�� �r(ji��)ֵ1000Ԫ������ARMϵ��ҕ�l������̳����r���t����

�r(ji��)ֵ1000Ԫ������ARMϵ��ҕ�l������̳����r���t���� �����¡�ARM�n���n�Ì�(sh��)䛾��A��ҕ�l���M(f��i)�I(l��ng)ȡ����(n��i)��Դ

�����¡�ARM�n���n�Ì�(sh��)䛾��A��ҕ�l���M(f��i)�I(l��ng)ȡ����(n��i)��Դ Ƕ��ʽ��(sh��)�r(sh��)����ϵ�y(t��ng)��RTOS���Еr(sh��)�g�|�l(f��)�c�¼��|�l(f��)���

Ƕ��ʽ��(sh��)�r(sh��)����ϵ�y(t��ng)��RTOS���Еr(sh��)�g�|�l(f��)�c�¼��|�l(f��)��� ����Arm Cortex-M55��������AIָ��U(ku��)չ�c�����{(di��o)��(y��u)

����Arm Cortex-M55��������AIָ��U(ku��)չ�c�����{(di��o)��(y��u) �����[ʽ��(j��ng)��ʾ��3D��(ch��ng)�����s�c��(sh��)�r(sh��)��Ⱦ���g(sh��)��(sh��)�`

�����[ʽ��(j��ng)��ʾ��3D��(ch��ng)�����s�c��(sh��)�r(sh��)��Ⱦ���g(sh��)��(sh��)�` Rust�Z(y��)������C(j��)Ƕ��ʽ�_(k��i)�l(f��)�е���ɱ������c��(n��i)�氲ȫ�(y��n)

Rust�Z(y��)������C(j��)Ƕ��ʽ�_(k��i)�l(f��)�е���ɱ������c��(n��i)�氲ȫ�(y��n) �Ԅ�(d��ng)���C(j��)���W(xu��)��(x��)(AutOML)��Ƕ��ʽҕ�X(ju��)�΄�(w��)�е�NAS���

�Ԅ�(d��ng)���C(j��)���W(xu��)��(x��)(AutOML)��Ƕ��ʽҕ�X(ju��)�΄�(w��)�е�NAS��� Zephyr RTOS�ڮ���(g��u)���̎�����е��΄�(w��)�����cؓ(f��)�d����

Zephyr RTOS�ڮ���(g��u)���̎�����е��΄�(w��)�����cؓ(f��)�d���� ���ڏ�(qi��ng)���W(xu��)��(x��)�ęC(j��)����·��Ҏ(gu��)���㷨��ROS�еČ�(sh��)�F(xi��n)�c��(y��u)

���ڏ�(qi��ng)���W(xu��)��(x��)�ęC(j��)����·��Ҏ(gu��)���㷨��ROS�еČ�(sh��)�F(xi��n)�c��(y��u) Ƕ��ʽLinuxϵ�y(t��ng)��eBPF���g(sh��)��(sh��)�F(xi��n)��(sh��)�r(sh��)�W(w��ng)�j(lu��)�����O(ji��n)��

Ƕ��ʽLinuxϵ�y(t��ng)��eBPF���g(sh��)��(sh��)�F(xi��n)��(sh��)�r(sh��)�W(w��ng)�j(lu��)�����O(ji��n)�� �����¼��(q��)��(d��ng)�Į���IO��܌�(sh��)�F(xi��n)�cЧ�ܷ���

�����¼��(q��)��(d��ng)�Į���IO��܌�(sh��)�F(xi��n)�cЧ�ܷ��� �������ɿ�¡���ܣ�PUF����Ƕ��ʽ�O(sh��)����������c����

�������ɿ�¡���ܣ�PUF����Ƕ��ʽ�O(sh��)����������c����